# **Application Note**

**BRT\_AN\_033**

# **BT81X Series Programming Guide**

Version 2.2

Issue Date: 24-09-2021

This application note describes the process and practice required to program BT81X Series, (BT815/6 and **BT817/8** chips).

# **Table of Contents**

| 1 I | ntro | duction                              | 11  |  |  |  |

|-----|------|--------------------------------------|-----|--|--|--|

| 1.1 | Sc   | оре                                  | .11 |  |  |  |

| 1.2 | In   | tended Audience                      | .11 |  |  |  |

| 1.3 | Co   | Conventions11                        |     |  |  |  |

| 1.4 | AF   | PI Reference Definitions             | .11 |  |  |  |

| 1.5 |      | hat's new in BT81X Series?           |     |  |  |  |

| 1.6 |      | hat is new in BT817/8?               |     |  |  |  |

|     |      | •                                    |     |  |  |  |

|     |      | ramming Model                        |     |  |  |  |

| 2.1 |      | ldress Space                         |     |  |  |  |

| 2.2 |      | ata Flow Diagram                     |     |  |  |  |

| 2.3 | Re   | ead Chip Identification Code (ID)    | .16 |  |  |  |

| 2.4 | In   | itialization Sequence during Boot Up | .16 |  |  |  |

| 2.5 | PV   | VM Control                           | .17 |  |  |  |

| 2.6 | RG   | GB Color Signal                      | .17 |  |  |  |

| 2.7 | To   | ouch Screen                          | .18 |  |  |  |

| 2.8 | Fla  | ash Interface                        | .19 |  |  |  |

| 2.9 | Αu   | ıdio Routines                        | .19 |  |  |  |

|     | 9.1  | Sound Effect                         |     |  |  |  |

| 2.9 | 9.2  | Audio Playback                       | 20  |  |  |  |

| 2.1 | 0 (  | Graphics Routines                    | .21 |  |  |  |

| 2.: | 10.1 | Getting Started                      |     |  |  |  |

| 2.: | 10.2 | Coordinate Range and Pixel Precision |     |  |  |  |

| 2.: | 10.3 | Screen Rotation                      | 22  |  |  |  |

| 2.: | 10.4 | Drawing Pattern                      | 24  |  |  |  |

| 2.: | 10.5 | Bitmap Transformation Matrix         | 26  |  |  |  |

| 2.: | 10.6 | Color and Transparency               | 26  |  |  |  |

| 2.  | 10.7 | Performance                          | 27  |  |  |  |

| 3 R | egi  | ster Description                     | 28  |  |  |  |

| 3.1 | Gr   | aphics Engine Registers              | .28 |  |  |  |

| 3.2  | Audio Engine Registers        | 32 |

|------|-------------------------------|----|

| 3.3  | Flash Registers               | 34 |

| 3.4  | Touch Screen Engine Registers | 35 |

| 3.4  | l.1 Overview                  | 35 |

| 3.4  | 1.2 Common Registers          | 35 |

| 3.4  | 1.3 Resistive Touch Engine    | 37 |

| 3.4  | 1.4 Capacitive Touch Engine   | 40 |

| 3.4  | l.5 Calibration               | 45 |

| 3.5  | Coprocessor Engine Registers  | 45 |

| 3.6  | Miscellaneous Registers       | 46 |

| 3.7  | Special Registers             | 51 |

| 4 Di | isplay List Commands          | 54 |

| 4.1  | Graphics State                | 54 |

| 4.2  | Command Encoding              |    |

|      | Command Groups                |    |

| 4.3  |                               |    |

| 4.3  |                               |    |

| 4.3  |                               |    |

| 4.4  | ALPHA_FUNC                    | 56 |

| 4.5  | BEGIN                         | 56 |

| 4.6  | BITMAP_EXT_FORMAT             | 57 |

|      | BITMAP_HANDLE                 |    |

|      | BITMAP_LAYOUT                 |    |

|      | BITMAP_LAYOUT_H               |    |

|      | DITMAP_LATOUT                 |    |

|      | <del>-</del>                  |    |

|      | L BITMAP_SIZE_H               |    |

|      | BITMAP_SOURCE                 |    |

|      | BITMAP_SWIZZLE                |    |

|      | 4 BITMAP_TRANSFORM_A          |    |

| 4.15 | BITMAP_TRANSFORM_B            | 69 |

| 4.16 | BITMAP_TRANSFORM_C | .69 |

|------|--------------------|-----|

| 4.17 | BITMAP_TRANSFORM_D | .70 |

| 4.18 | BITMAP_TRANSFORM_E | .70 |

| 4.19 | BITMAP_TRANSFORM_F | .71 |

| 4.20 | BLEND_FUNC         | .72 |

| 4.21 | CALL               | .73 |

| 4.22 | CELL               | .74 |

| 4.23 | CLEAR              | .74 |

| 4.24 | CLEAR_COLOR_A      | .75 |

| 4.25 | CLEAR_COLOR_RGB    | .76 |

| 4.26 | CLEAR_STENCIL      | .77 |

| 4.27 | CLEAR_TAG          | .77 |

| 4.28 | COLOR_A            | .77 |

| 4.29 | COLOR_MASK         | .78 |

| 4.30 | COLOR_RGB          | .79 |

| 4.31 | DISPLAY            | .80 |

| 4.32 | END                | .80 |

| 4.33 | JUMP               | .81 |

| 4.34 | LINE_WIDTH         | .81 |

| 4.35 | MACRO              | .82 |

| 4.36 | NOP                | .82 |

| 4.37 | PALETTE_SOURCE     | .83 |

| 4.38 | POINT_SIZE         | .83 |

| 4.39 | RESTORE_CONTEXT    | .84 |

| 4.40 | RETURN             | .85 |

| 4.41 | SAVE_CONTEXT       | .85 |

| 4.42 | SCISSOR_SIZE       | .86 |

| 4.43 | SCISSOR_XY         | .87 |

| 4.44 | STENCIL_FUNC       | .88 |

|      |                    |     |

| 4.45           | STENCIL_MASK                            | 88          |

|----------------|-----------------------------------------|-------------|

| 4.46           | STENCIL_OP                              | 89          |

| 4.47           | TAG                                     | 90          |

| 4.48           | TAG_MASK                                | 90          |

| 4.49           | VERTEX2F                                | 91          |

| 4.50           | VERTEX2II                               | 92          |

| 4.51           | VERTEX_FORMAT                           | 92          |

| 4.52           | VERTEX_TRANSLATE_X                      |             |

| 4.53           | VERTEX_TRANSLATE_Y                      |             |

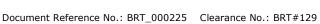

| 5 Сор          | rocessor Engine                         | 95          |

| 5.1 C          | ommand FIFO                             | 95          |

| 5.2 W          | /idgets                                 | 96          |

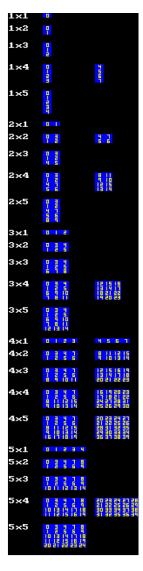

| 5.2.1          | Common Physical Dimensions              | 96          |

| 5.2.2          | Color Settings                          | 97          |

| 5.2.3          | Caveat                                  | 97          |

| 5.3 I          | nteraction with RAM_DL                  | 97          |

| 5.3.1          | Synchronization between MCU & Coprocess | or Engine98 |

| 5.4 R          | OM and RAM Fonts                        | 98          |

| 5.4.1          | Legacy Font Metrics Block               | 98          |

| 5.4.2          | Example to find the width of character  | 99          |

| 5.4.3          | Extended Font Metrics Block             |             |

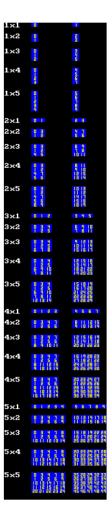

| 5.4.4          | ROM Fonts (Built-in Fonts)              |             |

| 5.4.5          | Using Custom Font                       |             |

|                | nimation support                        |             |

|                | tring Formatting                        |             |

| 5.6.1          | The Flag Characters                     |             |

| 5.6.2<br>5.6.3 | The Field Width  The Precision          |             |

| 5.6.4          | The Conversion Specifier                |             |

|                | oprocessor Faults                       |             |

|                | •                                       |             |

| J.0 C          | oprocessor Graphics State               |             |

| 5.9 I | Parameter OPTION      | 108 |

|-------|-----------------------|-----|

| 5.10  | Resources Utilization | 109 |

| 5.11  | Command list          | 109 |

| 5.12  | Command Groups        | 109 |

| 5.13  | CMD_APILEVEL          | 111 |

| 5.14  | CMD_DLSTART           | 111 |

| 5.15  | CMD_INTERRUPT         | 112 |

| 5.16  | CMD_COLDSTART         | 112 |

| 5.17  | CMD_SWAP              | 113 |

| 5.18  | CMD_APPEND            | 113 |

| 5.19  | CMD_REGREAD           | 114 |

| 5.20  | CMD_MEMWRITE          | 114 |

| 5.21  | CMD_INFLATE           | 115 |

| 5.22  | CMD_INFLATE2          | 116 |

| 5.23  | CMD_LOADIMAGE         | 116 |

| 5.24  | CMD_MEDIAFIFO         | 119 |

| 5.25  | CMD_PLAYVIDEO         | 119 |

| 5.26  | CMD_VIDEOSTART        | 120 |

| 5.27  | CMD_VIDEOFRAME        | 121 |

| 5.28  | CMD_MEMCRC            | 122 |

| 5.29  | CMD_MEMZERO           | 122 |

| 5.30  | CMD_MEMSET            | 123 |

| 5.31  | CMD_MEMCPY            | 123 |

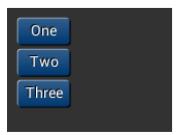

| 5.32  | CMD_BUTTON            | 124 |

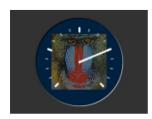

| 5.33  | CMD_CLOCK             | 125 |

| 5.34  | CMD_FGCOLOR           | 128 |

| 5.35  | CMD_BGCOLOR           | 129 |

| 5.36  | CMD_GRADCOLOR         | 129 |

| 5.37  | CMD_GAUGE             | 130 |

|       |                       |     |

| 5.38 | CMD_GRADIENT     | 133 |

|------|------------------|-----|

| 5.39 | CMD_GRADIENTA    | 135 |

| 5.40 | CMD_KEYS         | 136 |

| 5.41 | CMD_PROGRESS     | 139 |

| 5.42 | CMD_SCROLLBAR    | 140 |

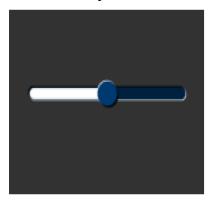

| 5.43 | CMD_SLIDER       | 142 |

| 5.44 | CMD_DIAL         | 143 |

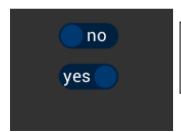

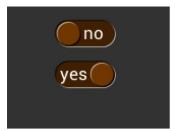

| 5.45 | CMD_TOGGLE       | 145 |

| 5.46 | CMD_FILLWIDTH    | 146 |

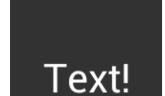

| 5.47 | CMD_TEXT         | 147 |

| 5.48 | CMD_SETBASE      |     |

| 5.49 | CMD_NUMBER       | 150 |

| 5.50 | CMD_LOADIDENTITY | 151 |

| 5.51 | CMD_SETMATRIX    | 151 |

| 5.52 | CMD_GETMATRIX    | 152 |

| 5.53 | CMD_GETPTR       | 152 |

| 5.54 | CMD_GETPROPS     | 153 |

| 5.55 | CMD_SCALE        | 154 |

| 5.56 | CMD_ROTATE       | 155 |

| 5.57 | CMD_ROTATEAROUND | 156 |

| 5.58 | CMD_TRANSLATE    | 157 |

| 5.59 | CMD_CALIBRATE    | 158 |

| 5.60 | CMD_CALIBRATESUB | 158 |

| 5.61 | CMD_SETROTATE    | 159 |

| 5.62 | CMD_SPINNER      | 160 |

| 5.63 | CMD_SCREENSAVER  | 161 |

| 5.64 | CMD_SKETCH       | 162 |

| 5.65 | CMD_STOP         | 163 |

| 5.66 | CMD_SETFONT      | 164 |

|      |                  |     |

| 5.67 | CMD_SETFONT2      | 164 |

|------|-------------------|-----|

| 5.68 | CMD_SETSCRATCH    | 165 |

| 5.69 | CMD_ROMFONT       | 166 |

| 5.70 | CMD_RESETFONTS    | 166 |

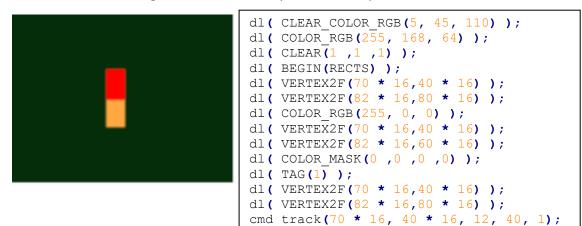

| 5.71 | CMD_TRACK         | 167 |

| 5.72 | CMD_SNAPSHOT      | 170 |

| 5.73 | CMD_SNAPSHOT2     | 170 |

| 5.74 | CMD_SETBITMAP     | 172 |

| 5.75 | CMD_LOGO          | 173 |

| 5.76 | CMD_FLASHERASE    | 173 |

| 5.77 | CMD_FLASHWRITE    | 173 |

| 5.78 | CMD_FLASHPROGRAM  | 174 |

| 5.79 | CMD_FLASHREAD     | 175 |

| 5.80 | CMD_APPENDF       | 175 |

| 5.81 | CMD_FLASHUPDATE   | 176 |

| 5.82 | CMD_FLASHDETACH   | 176 |

| 5.83 | CMD_FLASHATTACH   | 177 |

| 5.84 | CMD_FLASHFAST     | 177 |

| 5.85 | CMD_FLASHSPIDESEL | 178 |

| 5.86 | CMD_FLASHSPITX    | 178 |

| 5.87 | CMD_FLASHSPIRX    | 178 |

| 5.88 | CMD_CLEARCACHE    | 179 |

| 5.89 | CMD_FLASHSOURCE   | 180 |

| 5.90 | CMD_VIDEOSTARTF   | 180 |

| 5.91 | CMD_ANIMSTART     | 180 |

| 5.92 | CMD_ANIMSTARTRAM  | 181 |

| 5.93 | CMD_RUNANIM       | 182 |

| 5.94 | CMD_ANIMSTOP      | 183 |

| 5.95 | CMD_ANIMXY        | 184 |

|      |                   |     |

| 5.96               | CMD_ANIMDRAW                                  | 184  |  |  |

|--------------------|-----------------------------------------------|------|--|--|

| 5.97               | CMD_ANIMFRAME                                 | 184  |  |  |

| 5.98               | CMD_ANIMFRAMERAM                              | 185  |  |  |

| 5.99               | CMD_SYNC                                      | 186  |  |  |

| 5.100              | CMD_BITMAP_TRANSFORM                          | 187  |  |  |

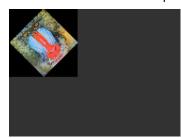

| 5.101              | CMD_TESTCARD                                  | 188  |  |  |

| 5.102              | CMD_WAIT                                      | 189  |  |  |

| 5.103              | CMD_NEWLIST                                   | 189  |  |  |

| 5.104              | CMD_ENDLIST                                   | 190  |  |  |

| 5.105              | CMD_CALLLIST                                  | 191  |  |  |

| 5.106              | CMD_RETURN                                    | 191  |  |  |

| 5.107              | CMD_FONTCACHE                                 | 192  |  |  |

| 5.108              | CMD_FONTCACHEQUERY                            | 193  |  |  |

| 5.109              | CMD_GETIMAGE                                  | 193  |  |  |

| 5.110              | CMD_HSF                                       | 194  |  |  |

| 5.111              | CMD_PCLKFREQ                                  | 195  |  |  |

| 6 AST              | C                                             | 197  |  |  |

| 6.1 A              | STC RAM Layout                                | 197  |  |  |

| 6.2 A              | STC Flash Layout                              | 198  |  |  |

| 7 Con              | tact Information                              | 199  |  |  |

| Appen              | dix A – References                            | 200  |  |  |

| Docun              | nent References                               | 200  |  |  |

| Acron              | yms and Abbreviations                         | 200  |  |  |

| Appen              | dix B – List of Tables/ Figures/ Registers/ ( | Code |  |  |

| Snippe             | ets                                           | 201  |  |  |

| List of            | Tables                                        | 201  |  |  |

| List of Figures201 |                                               |      |  |  |

| List of            | Registers                                     | 202  |  |  |

| List of            | Code Snippets                                 | 204  |  |  |

|                    |                                               |      |  |  |

Appendix C - Revision History ...... 206

# 1 Introduction

This document captures the programming details for the **BT81X** Series chips (BT815/6, BT817/8) including graphics commands, widget commands and configurations to control **BT81X** Series chips for smooth and vibrant screen effects.

The **BT81X** Series chips are graphics controllers with add-on features such as audio playback and touch capabilities. They consist of a rich set of graphics objects that can be used for displaying various menus and screen shots for a range of products including home appliances, toys, industrial machinery, home automation, elevators, and many more.

# 1.1 Scope

This document will be useful to understand the command set and demonstrate the ease of usage in the examples given for each specific instruction. In addition, it also covers various power modes, audio, and touch features as well as their usage.

The descriptions in this document are applicable to both BT815/6 and BT817/8, unless specified otherwise.

Within this document, the endianness of commands, register values, and data in  ${\bf RAM\_G}$  are in *little-endian* format.

Information on pin settings, hardware characteristics and hardware configurations can be found in the BT815/6 or **BT817/8** data sheet.

### 1.2 Intended Audience

The intended audience of this document are Software Programmers and System Designers who develop graphical user interface (**GUI**) applications on any processor with an **SPI** master interface.

# 1.3 Conventions

All values are in decimal by default.

The values with **0x** are in hexadecimal.

The values with **0b'** are in binary.

Host refers to the MCU/MPU with SPI master interface connecting with EVE.

Host commands refer to the **EVE** specific commands defined in the Serial Data Protocol section of the datasheet.

## 1.4 API Reference Definitions

The following table provides the functionality and nomenclature of the APIs used in this document.

| wr8() write 8 bits to intended address location |                                             |  |

|-------------------------------------------------|---------------------------------------------|--|

| wr16()                                          | write 16 bits to intended address location  |  |

| wr32()                                          | write 32 bits to intended address location  |  |

| rd8()                                           | read 8 bits from intended address location  |  |

| rd16()                                          | read 16 bits from intended address location |  |

Document Reference No.: BRT\_000225 Clearance No.: BRT#129

| rd32() read 32 bits from intended address location |                                                                                                   |  |  |  |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|

| cmd()                                              | write 32 bits data to command <b>FIFO</b> i.e. <b>RAM_CMD</b>                                     |  |  |  |

| cmd_*()                                            | Write 32 bits commands with its necessary parameters to command <b>FIFO</b> i.e. <b>RAM_CMD</b> . |  |  |  |

| dl()                                               | Write 32 bits display list command to <b>RAM_DL</b> .                                             |  |  |  |

| host_command()                                     | send host command in host command protocol                                                        |  |  |  |

Table 1 - API Reference Definitions

# 1.5 What's new in BT81X Series?

Compared to the previous generation FT81X series, the BT81X Series introduces several enhanced features:

- QSPI NOR flash interface \*

- Adaptive Scalable Texture Compression(ASTC) format bitmap \*

- Unicode text display \*

- Animation support

The tables below captures the new and updated commands in BT81X for these features:

| <b>Coprocessor Commands</b>                                                                                                                                               | BT81X   | Remarks                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------------|

| CMD_ANIMDRAW CMD_ANIMFRAME CMD_ANIMSTART CMD_ANIMSTOP CMD_ANIMXY                                                                                                          | New     | Animation feature related coprocessor commands                          |

| CMD_APPENDF                                                                                                                                                               | New     | Append flash data to display list                                       |

| CMD_CLEARCACHE                                                                                                                                                            | New     | Clear the flash cache                                                   |

| CMD_FLASHATTACH CMD_FLASHDETACH CMD_FLASHERASE CMD_FLASHFAST CMD_FLASHREAD CMD_FLASHSOURCE CMD_FLASHSPIDESEL CMD_FLASHSPIRX CMD_FLASHSPITX CMD_FLASHUPDATE CMD_FLASHWRITE | New     | Flash interface operation related coprocessor commands                  |

| CMD_FILLWIDTH                                                                                                                                                             | New     | Set the line width for the text of cmd_text and cmd_button              |

| CMD_GRADIENTA                                                                                                                                                             | New     | Draw a smooth color gradient with transparency                          |

| CMD_INFLATE2                                                                                                                                                              | New     | Decompress data into memory with more options: OPT_FLASH, OPT_MEDIAFIFO |

| CMD_RESETFONTS                                                                                                                                                            | New     | Loads a ROM font into a bitmap handle                                   |

| CMD_ROTATEAROUND                                                                                                                                                          | New     | Apply a rotation and scale around (x,y) for bitmap                      |

| CMD_VIDEOSTARTF                                                                                                                                                           | New     | Initialize video frame decoder for the data in flash memory             |

| CMD_TEXT<br>CMD_BUTTON<br>CMD_TOGGLE                                                                                                                                      | Changed | Added option : OPT_FORMAT                                               |

Document Reference No.: BRT\_000225 Clearance No.: BRT#129

| CMD_LOADIMAGE<br>CMD_PLAYVIDEO<br>CMD_VIDEOSTARTF                                    | Changed | Supports data stored in flash                                           |

|--------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------------|

| Display List                                                                         | BT81X   | Remarks                                                                 |

| BITMAP_SOURCE                                                                        | Changed | Expand the address bit field to access <b>ASTC</b> bitmap in flash      |

| BITMAP_TRANSFORM_A<br>BITMAP_TRANSFORM_B<br>BITMAP_TRANSFORM_D<br>BITMAP_TRANSFORM_E | Changed | Added new precision control : signed fixed point 1.15                   |

| BITMAP_LAYOUT                                                                        | Changed | Added a new valid value for format parameter: GLFORMAT                  |

| BITMAP_EXT_FORMAT                                                                    | New     | Support more bitmap formats, especially <b>ASTC</b> compression formats |

| BITMAP_SWIZZLE                                                                       | New     | Set the source for the r,g,b,a channels of a bitmap                     |

Table 2 - Updated Commands in BT81X

# 1.6 What is new in BT817/8?

BT817/8 maintains backward compatibility with the previous BT815/6 ICs. Any application built for BT815/6 is able to run on the BT817/8 series without any changes. In short, BT817/8 is an improved version of BT815/6.

Compared to BT815/6, BT817/8 has a 1.5x graphics engine performance improvement. In addition, it introduces many enhancements including:

- Programmable timing to adjust HSYNC and VSYNC timing, enabling interface to numerous displays

- Add Horizontal Scan out Filter to support non-square pixel LCD display

- Adaptive Hsync mode to delay the start of scanout line while keeping PCLK running

- Supports Animation in RAM\_G

- Enable constructing command list in RAM\_G

- New font cache mechanism for custom fonts whose glyph is in flash

To facilitate the features above, there are the new registers and commands introduced for the BT817/8. They can be found in this document with the note "BT817/8 specific".

Besides that, two commands in BT815/6 are improved in BT817/8:

- CMD\_GETPTR

- CMD\_GETPROPS

However, these two commands are kept in same functionality for compatibility unless CMD\_APILEVEL is sent with parameter level 2.

Document Reference No.: BRT\_000225 Clearance No.: BRT#129

# 2 Programming Model

**EVE** appears to the host MCU as a memory-mapped SPI device. The host MCU sends commands and data over the serial protocol described in the data sheet.

#### 2.1 **Address Space**

All memory and registers are memory mapped into 22-bit address space with a 2-bit SPI command prefix: Prefix 0'b00 for read and 0'b10 for write to the address space, 0'b01is reserved for Host Commands and 0'b11 undefined. Please refer to the datasheet about the serial data protocol used to read/write these addresses. The memory space definitions are provided in the following table:

| Name           | Start<br>Address | End<br>Address                                              | Size<br>(bytes) | Description                                                                                                                                                                                                     |

|----------------|------------------|-------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAM_G          | 0x000000         | 0x0FFFFF                                                    | 1024 Ki         | General purpose graphics <b>RAM</b> , also called main memory in this document                                                                                                                                  |

| ROM_FONT       | 0x1E0000         | 0x2FFFFB                                                    | 1152 Ki         | Font table and bitmap                                                                                                                                                                                           |

| ROM_FONTROOT   | 0x2FFFFC         | 0x2FFFFF                                                    | 4               | Font table pointer address                                                                                                                                                                                      |

| RAM_DL         | 0x300000         | 0x301FFF                                                    | 8 Ki            | Display list RAM                                                                                                                                                                                                |

| RAM_REG        | 0x302000         | 0x302FFF                                                    | 4 Ki            | Registers                                                                                                                                                                                                       |

| RAM_CMD        | 0x308000         | 0x308FFF                                                    | 4 Ki            | Command <b>FIFO</b>                                                                                                                                                                                             |

| RAM_ERR_REPORT | 0x309800         | 0x3098FF                                                    | 128             | Coprocessor fault report area                                                                                                                                                                                   |

| Flash memory   | 0x800000         | Depending on<br>attached flash<br>chip, up to<br>0x107FFFFF | Up to<br>256Mi  | External NOR flash memory. It can <b>NOT</b> be addressed by <b>host</b> directly.  The address is used by the following commands only for rendering <b>ASTC</b> image only: <b>CMD_SETBITMAP BITMAP_SOURCE</b> |

Table 3 – Memory Map

### Note:

- 1. The addresses beyond this table are reserved and shall not be read or written unless otherwise specified.

- To access the flash memory, host needs leverage the coprocessor commands, such as

- CMD\_FLASHREAD

- CMD\_FLASHWRITE

- CMD\_FLASHUPDATE

These commands uses zero based address to address the blocks of flash. See Flash Interface for more details.

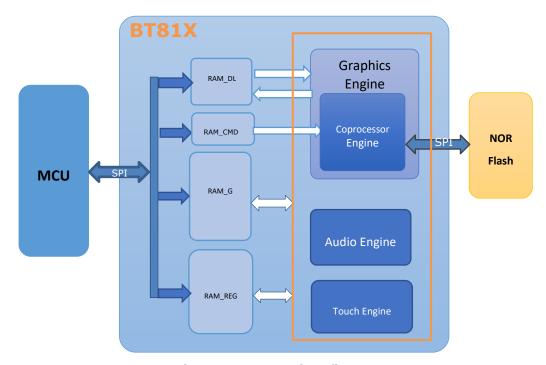

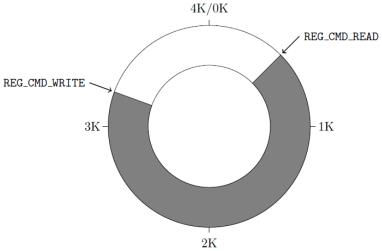

# 2.2 Data Flow Diagram

Figure 1 describes the data flow between 1) **external components** (MCU and Flash) 2) **internal components of EVE**. Please note that the direct write from **MCU** to **RAM\_DL** requires careful actions to sync up the read/write pointers in the respective registers of **EVE** because coprocessor engine may also write the generated display list commands into **RAM\_DL**.

To save such effort, the better approach is to write the display list command to **RAM\_CMD** and make coprocessor update the **RAM\_DL** accordingly.

Figure 1 - BT81X data flow

The data here refers to the following items:

- **Display list :** Instructions for graphics engine to render the screen

- **Coprocessor command:** Predefined commands by coprocessor engine

- Bitmap data: Pixel representation in EVE defined formats: such as RGB565, ASTC etc.

- **JPEG/PNG stream:** Image data in PNG/JPEG format conforming to Eve requirement, for coprocessor engine to decode.

- **MJPEG stream:** The video data in MJPEG format conforming to Eve requirement for coprocessor engine to decode.

- Audio stream: uLaw, ADPCM, PCM encoded audio samples, for audio engine to decode

- Flash image: data to be programmed into flash or data read back from flash.

- **Register values:** read or write the registers.

# 2.3 Read Chip Identification Code (ID)

After reset or reboot, the chip ID can be read from address 0xC0000 to 0xC0003.

To read the chip identification code, users shall read 4 bytes of data from address 0xC0000 before the application overwrites this address, since it is located in **RAM\_G**.

The following table describes the data to be read:

| 0xC0003 | 0xC0002 | 0xC0001        | 0xC0000 |

|---------|---------|----------------|---------|

| 0x00    | 0x01    | 0x10 for FT810 | 0x08    |

|         |         | 0x11 for FT811 |         |

|         |         | 0x12 for FT812 |         |

|         |         | 0x13 for FT813 |         |

|         |         | 0x15 for BT815 |         |

|         |         | 0x16 for BT816 |         |

|         |         | 0x17 for BT817 |         |

|         |         | 0x18 for BT818 |         |

Table 4 - Read Chip Identification Code

# 2.4 Initialization Sequence during Boot Up

During EVE boot up, the following steps are required:

- Send host command "CLKEXT" if the PLL input is from external crystal oscillator or external clock.

- 2. Send host command "CLKSEL" to select system clock frequency if the non-default system clock is to be used.

- By default the system clock is set to 60MHz. However, 72MHz is recommended for better performance.

- 3. Send Host command "ACTIVE".

- 4. Send Host command "RST\_PULSE"

- 5. Read **REG\_ID** until **0x7C** is returned.

- 6. Read **REG\_CPURESET** till **EVE** goes into the working status, i.e., zero is returned.

- 7. Configure display control timing registers, except **REG\_PCLK**

- 8. Write first display list to **RAM\_DL**.

- 9. Write REG\_DLSWAP to start graphics engine rendering process with first display list

- 10. Enable backlight control for display panel

- 11. Write **REG\_PCLK** to configure the PCLK frequency of display panel, which leads to the output of the first display list

```

host command (CLKEXT); //send command "CLKEXT" to use the external clock source

host command(CLKSEL);//select the system clock frequency

host_command(ACTIVE);//send host command "ACTIVE" to wake up

msWait(300);

//wait 300 milliseconds

while (0 \times 7C != rd8 (REG ID));

while (0x0 != rd16 (REG CPURESET)); //Check if EVE is in working status.

wr32(REG FREQUENCY, 0x3938700); //Configure the system clock to 60MHz.

^{\prime \star} Configure display registers - demonstration for WVGA 800x480 resolution ^{\star \prime}

wr16 (REG HCYCLE, 928);

wr16 (REG HOFFSET, 88);

wr16(REG_HSYNCO, 0);

wr16(REG_HSYNC1, 48);

wr16(REG_VCYCLE, 525);

wr16(REG_VOFFSET, 32);

wr16(REG_VSYNCO, 0);

wr16(REG VSYNC1, 3);

wr8(REG SWIZZLE, 0);

wr8(REG_PCLK_POL, 1);

```

Document Reference No.: BRT\_000225 Clearance No.: BRT#129

```

wr8 (REG CSPREAD, 0);

wr16(REG_HSIZE, 800);

wr16(REG_VSIZE, 480);

^{\prime \star} Write first display list to display list memory RAM_DL*/

wr32 (RAM DL+0, CLEAR COLOR RGB (0,0,0));

wr32(RAM DL+4,CLEAR(1,1,1));

wr32(RAM DL+8, DISPLAY());

wr8(REG DLSWAP, DLSWAP FRAME);//display list swap

/* Enable backlight of display panel */

#if defined(FT81X ENABLE)

wr16(REG_GPIOX_DIR, 0xffff);

wr16(REG_GPIOX, 0xffff);

#else

wr8 (REG GPIO DIR, 0xff);

wr8 (REG GPIO, 0xff);

#endif

wr8(REG PCLK,2); //Configure the PCLK divisor to 2, i.e. PCLK = System CLK/2

```

Code Snippet 1 - Initialization Sequence

### 2.5 PWM Control

The PWM signal is controlled by two registers: REG\_PWM\_HZ and REG\_PWM\_DUTY.

**REG\_PWM\_HZ** specifies the PWM output frequency.

**REG\_PWM\_DUTY** specifies the PWM output duty cycle.

# 2.6 RGB Color Signal

The RGB color signal is carried over 24 signals - 8 each for red, green and blue. Several registers affect the operation of these signals. The order of these operations in the display output system is as follows:

**REG\_DITHER** enables color dither. To improve the image quality, **EVE** applies a 2×2 color dither matrix to output pixels. The dither option improves half-tone appearance on displays, even on 1bit displays.

REG\_OUTBITS gives the bit width of each color channel. The default is zero, meaning 8 bits each channel. Lower values mean that fewer bits are output for the color channel. This value also affects dither computation.

REG\_SWIZZLE controls the arrangement of the output color pins, to help PCB routing with different LCD panel arrangements. Bit 0 of the register causes the order of bits in each color channel to be reversed. Bits 1-3 control the RGB order. Bit 1 set causes R and B channels to be swapped. Bit 3 is rotate enable. If bit 3 is set, then (R, G, B) is rotated right if bit 2 is one, or left if bit 2 is zero. Please refer to BT817/8 datasheet for more details.

### 2.7 Touch Screen

The raw touch screen (x, y) values are available in register **REG\_TOUCH\_RAW\_XY**. The range of these values is 0-1023. If the touch screen is not being pressed, both registers read 0xFFFF.

These touch values are transformed into screen coordinates using the matrix in registers **REG\_TOUCH\_TRANSFORM\_A-F**. The post-transform coordinates are available in register **REG\_TOUCH\_SCREEN\_XY**. If the touch screen is not being pressed, both registers read 0x8000 (-32768). The values for **REG\_TOUCH\_TRANSFORM A-F** may be computed using an on-screen calibration process. If the screen is being touched, the screen coordinates are looked up in the screen's tag buffer, delivering a final 8-bit tag value, in **REG\_TOUCH\_TAG**. Because the tag lookup takes a full frame, and touch coordinates change continuously, the original (x, y) used for the tag lookup is also available in **REG\_TOUCH\_TAG\_XY**.

Screen touch pressure is available in **REG\_TOUCH\_RZ**. This register gives the resistance of the touch screen press, so lower values indicate more pressure. The register's range is 0 (maximum pressure) to 32767 (no touch). Because the values depend on the particular screen, and the instrument used for pressing (stylus, fingertip, gloved finger, etc.) a calibration or setup step shall be used to discover the useful range of resistance values.

**REG\_TOUCH\_MODE** controls the frequency of touch sampling. **TOUCHMODE\_CONTINUOUS** is continuous sampling. Writing **TOUCHMODE\_ONESHOT** causes a single sample to occur. **TOUCHMODE\_FRAME** causes a sample at the start of each frame. **TOUCHMODE\_OFF** stops all sampling.

**REG\_TOUCH\_ADC\_MODE** selects single-ended (**ADC\_SINGLE\_ENDED**) or differential (**ADC\_DIFFERENTIAL**) ADC operation. Single-ended consumes less power, differential gives more accurate positioning. **REG\_TOUCH\_CHARGE** specifies how long to drive the touchscreen voltage before sampling the pen detect input. The default value 3000 gives a delay of 0.3ms which is suitable for most screens.

**REG\_TOUCH\_RZTHRESH** specifies a threshold for touchscreen resistance. If the measured touchscreen resistance is greater than this threshold, then no touch is reported. The default value is 65535, so all touches are reported.

**REG\_TOUCH\_SETTLE** specifies how long to drive the touchscreen voltage before sampling the position. For screens with a large capacitance, this value should be increased. For low capacitance screens this value can be decreased to reduce "on" time and save power.

**REG\_TOUCH\_OVERSAMPLE** controls the oversampling factor used by the touchscreen system. Increase this value to improve noise rejection if necessary. For systems with low noise, this value can be lowered to reduce "on" time and save power.

Touch screen 32-bit register updates are atomic: all 32 bits are updated in a single cycle. So when reading an XY register, for example, both (x, y) values are guaranteed to be from the same sensing cycle. When the sensing cycle is complete, and the registers have been updated, the **INT\_CONV\_COMPLETE** interrupt is triggered.

As well as the above high-level samples, the direct 10-bit **ADC** values are available in two registers, **REG\_TOUCH\_DIRECT\_XY** and **REG\_TOUCH\_DIRECT\_Z1Z2**. These registers are laid out as follows:

| 31 | 30 | 29 | 28 | <b>27</b> | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|-----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| S  |    |    |    |           |    |    |    |    |    | 2  | ζ. |    |    |    |    |    |    |    |    |    |    |   |   |   |   | 7 | 7 |   |   |   |   |

|    |    |    |    |           |    |    |    |    |    | Z  | 1  |    |    |    |    |    |    |    |    |    |    |   |   |   |   | Z | 2 |   |   |   |   |

The S field is 0 if a touch is being sensed, in which case all fields hold their sensed values. If S is 1, then no touch is sensed and all fields should be ignored.

# 2.8 Flash Interface

To access an attached flash chip, **EVE** provides the necessary registers to read/write flash with very high throughput. The graphics engine can fetch these graphics assets directly without going through the external host MCU, thus significantly off-loading the host MCU from feeding display contents.

The register REG\_FLASH\_STATUS indicates the state of the flash subsystem. During boot up, the flash state is FLASH\_STATE\_INIT. After detection has completed, flash is in the state FLASH\_STATE\_DETACHED or FLASH\_STATE\_BASIC, depending on whether an attached flash device was detected. If no device is detected, then all the SPI output signals are driven low. When the host MCU calls CMD\_FLASHFAST, the flash system attempts to go to full-speed mode, setting the state to FLASH\_STATE\_FULL. At any time, users can call CMD\_FLASHDETACH in order to disable the flash communications. This tri-states all flash signals, allowing a suitably connected MCU to drive the flash directly. Alternatively, in the detached state, commands CMD\_FLASHSPIDESEL, CMD\_FLASHSPITX and CMD\_FLASHSPIRX can be used to control the SPI bus. If detached, the host MCU can call CMD\_FLASHATTACH to re-establish communication with the flash device. Direct rendering of ASTC based bitmaps from flash is only possible in FLASH\_STATE\_FULL. After modifying the contents of flash, the MCU should clear the on-chip bitmap cache by calling CMD\_CLEARCACHE.

| Command           | DETACHED | BASIC    | FULL     | Operation                             |

|-------------------|----------|----------|----------|---------------------------------------|

| CMD_FLASHERASE    |          | <b>√</b> | <b>√</b> | Erase all of flash                    |

| CMD_FLASHWRITE    |          | <b>√</b> | ✓        | Write data from <b>RAM_CMD</b> to     |

|                   |          |          |          | blank flash                           |

| CMD_FLASHUPDATE   |          | ✓        | ✓        | Read the flash and update to          |

|                   |          |          |          | flash if different                    |

| CMD_FLASHPROGRAM  |          | ✓        | ✓        | Write data from <b>RAM_G</b> to blank |

|                   |          |          |          | flash                                 |

| CMD_FLASHREAD     |          | ✓        | ✓        | Reads data from flash to main         |

|                   |          |          |          | memory                                |

| CMD_FLASHDETACH   |          | <b>√</b> | ✓        | Detach from flash                     |

| CMD_FLASHATTACH   | ✓        |          |          | Attach to flash                       |

| CMD_FLASHFAST     |          | ✓        |          | Enter full-speed(fast) mode           |

| CMD_FLASHSPIDESEL | <b>✓</b> |          |          | SPI bus: deselect device              |

| CMD_FLASHSPITX    | ✓        |          |          | SPI bus: write bytes                  |

| CMD_FLASHSPIRX    | <b>✓</b> |          |          | SPI bus: read bytes                   |

Table 5 - Flash Interface states and commands

To support different vendors of SPI NOR flash chips, the first block (4096 bytes) of the flash is reserved for the flash driver called **BLOB** file which is provided by **Bridgetek**. The **BLOB** file shall be programmed first so that flash state can enter into full-speed (fast) mode. Please refer to BT81x datasheet for more details.

### 2.9 Audio Routines

The audio engine has two functionalities: synthesize built-in sound effects with selected pitches and play back the audio data in **RAM\_G**.

### 2.9.1 Sound Effect

The audio engine has various sound data built-in to work as a sound synthesizer. Sample code to play C8 on the xylophone:

```

wr8(REG_VOL_SOUND, 0xFF); //set the volume to maximum wr16(REG_SOUND, (0x6C<< 8) | 0x41); // C8 MIDI note on xylophone wr8(REG_PLAY, 1); // play the sound

```

Code Snippet 2 - Play C8 on the Xylophone

Version 2.2

Document Reference No.: BRT\_000225 Clearance No.: BRT#129

### Sample code to stop sound play:

```

wr16(REG_SOUND,0x0);//configure "silence" sound to be played

wr8(REG_PLAY,1);//play sound

Sound_status = rd8(REG_PLAY);//1-play is going on, 0-play has finished

```

### Code snippet 3 - Stop Playing Sound

To avoid a pop sound on reset or power state change, trigger a "mute" sound, and wait for it to complete (i.e. **REG\_PLAY** contains the value of 0). This sets the audio output pin to 0 levels. On reboot, the audio engine plays back the "unmute" sound.

```

wr16(REG_SOUND,0x60);//configure "mute" sound to be played

wr8(REG_PLAY,1);//play sound

Sound_status = rd8(REG_PLAY);//1-play is going on, 0-play has finished

```

### Code snippet 4 - Avoid Pop Sound

**Note:** Refer to BT817/8 datasheet for more information on the sound synthesizer and audio playback.

### 2.9.2 Audio Playback

The audio engine supports an audio playback feature. For the audio data in the **RAM\_G** to play back, it requires the start address in **REG\_PLAYBACK\_START** to be 8 bytes aligned. In addition, the length of audio data specified by **REG\_PLAYBACK\_LENGTH** is required to be 8 bytes aligned.

Three types of audio formats are supported: 4 Bit IMA ADPCM, 8 Bit signed PCM, 8 Bit u-Law. For IMA ADPCM format, please note the byte order: within one byte, the first sample (4 bits) shall be located from bit 0 to bit 3, while the second sample (4 bits) shall be located from bit 4 to bit 7.

To learn how to play back the audio data, please check the sample code below:

```

wr8 (REG_VOL_PB, 0xFF);//configure audio playback volume wr32 (REG_PLAYBACK_START,0);//configure audio buffer starting address wr32 (REG_PLAYBACK_LENGTH,100*1024);//configure audio buffer length wr16 (REG_PLAYBACK_FREQ,44100);//configure audio sampling frequency wr8 (REG_PLAYBACK_FORMAT,ULAW_SAMPLES);//configure audio format wr8 (REG_PLAYBACK_LOOP,0);//configure once or continuous playback wr8 (REG_PLAYBACK_PLAY,1);//start the audio playback

```

### Code Snippet 5 – Audio Playback

```

AudioPlay_Status = rd8(REG_PLAYBACK_PLAY);//1-audio playback is going on, 0-audio playback has finished

```

# Code Snippet 6 - Check the status of Audio Playback

```

wr32(REG_PLAYBACK_LENGTH,0);//configure the playback length to 0 wr8(REG_PLAYBACK_PLAY,1); //start audio playback

```

### Code Snippet 7 - Stop the Audio Playback

# 2.10 Graphics Routines

This section describes graphics features and captures a few examples. Please note that the code in this section is for the purpose of illustrating the operation of Display Lists. Application will normally send the commands via **command FIFO (RAM\_CMD)** instead of writing directly to **RAM\_DL**.

# 2.10.1 Getting Started

The following example creates a screen with the text "TEXT" on it, with a red dot.

Figure 2 - Getting Started Example

The code to draw the screen is:

Code Snippet 8 - Getting Started

Upon loading the above drawing commands into **RAM\_DL**, register **REG\_DLSWAP** is required to be set to **0x02** in order to make the new display list active on the next frame refresh.

### Note:

- The display list always starts at address RAM\_DL

- The address always increments by 4 bytes as each command is 32 bits wide.

- Command CLEAR is recommended to be used before any other drawing operation, in order to put the graphics engine in a known state. The end of the display list is always flagged with the command DISPLAY

# 2.10.2 Coordinate Range and Pixel Precision

Apart from the single pixel precision, **EVE** support a series of fractional pixel precision, which result in a different coordinate range. Users may trade the coordinate range against pixel precision. See **VERTEX\_FORMAT** for more details.

Please note that the maximum screen resolution which **EVE** can render is up to 2048 by 2048 in pixels only, regardless of which pixel precision is specified.

**VERTEX2F** and **VERTEX\_FORMAT** are the commands that enable the drawing operation to reach the full coordinate plane. The **VERTEX2II** command only allows positive screen coordinates. The **VERTEX2F** command allows negative coordinates. If the bitmap is partially off-screen, for example during a screen scroll, then it is necessary to specify negative screen coordinates.

### 2.10.3 Screen Rotation

**REG\_ROTATE** controls the screen orientation. Changing the register value immediately causes the orientation of the screen to change. In addition, the coordinate system is also changed accordingly, so that all the display commands and coprocessor commands work in the rotated coordinate system.

**Note:** The touch transformation matrix is not affected by setting **REG\_ROTATE**.

To adjust the touch screen accordingly, users are recommended to use **CMD SETROTATE** as opposed to setting **REG\_ROTATE**.

REG\_ROTATE = 0 is the default landscape orientation:

REG ROTATE = 1 is inverted landscape:

REG\_ROTATE = 2 is portrait:

Document Reference No.: BRT\_000225 Clearance No.: BRT#129

REG\_ROTATE = 3 is inverted portrait:

REG\_ROTATE = 4 is mirrored landscape:

REG\_ROTATE = 5 is mirrored inverted landscape:

REG\_ROTATE = 6 is mirrored portrait:

REG\_ROTATE = 7 is mirrored inverted portrait:

### Version 2.2

Document Reference No.: BRT\_000225 Clearance No.: BRT#129

# 2.10.4 Drawing Pattern

The general pattern for drawing is driven by display list commands:

- BEGIN with one of the primitive types

- Input one or more vertices using "VERTEX2II" or "VERTEX2F", which specify the

placement of the primitive on the screen

- END to mark the end of the primitive.

### **Examples**

Draw points with varying radius from 5 pixels to 13 pixels with different colors:

```

//The VERTEX2F command gives the location of the circle center dl( COLOR_RGB(128, 0, 0) ); dl( POINT_SIZE(5 * 16) ); dl( BEGIN(POINTS) ); dl( VERTEX2F(30 * 16,17 * 16) ); dl( COLOR_RGB(0, 128, 0) ); dl( POINT_SIZE(8 * 16) ); dl( VERTEX2F(90 * 16, 17 * 16) ); dl( COLOR_RGB(0, 0, 128) ); dl( POINT_SIZE(10 * 16) ); dl( VERTEX2F(30 * 16, 51 * 16) ); dl( VERTEX2F(30 * 16, 51 * 16) ); dl( POINT_SIZE(13 * 16) ); dl( POINT_SIZE(13 * 16) ); dl( VERTEX2F(90 * 16, 51 * 16) );

```

Draw lines with varying sizes from 2 pixels to 6 pixels with different colors (line width size is from the center of the line to the boundary):

```

//The VERTEX2F commands are in pairs to define the start and finish point of the line. dl(COLOR_RGB(128, 0, 0)); dl(LINE_WIDTH(2 * 16)); dl(BEGIN(LINES)); dl(VERTEX2F(30 * 16,38 * 16)); dl(VERTEX2F(30 * 16,63 * 16)); dl(COLOR_RGB(0, 128, 0)); dl(LINE_WIDTH(4 * 16)); dl(VERTEX2F(60 * 16,25 * 16)); dl(VERTEX2F(60 * 16,63 * 16)); dl(VERTEX2F(60 * 16,63 * 16)); dl(COLOR_RGB(128, 128, 0)); dl(LINE_WIDTH(6 * 16)); dl(VERTEX2F(90 * 16, 13 * 16)); dl(VERTEX2F(90 * 16, 63 * 16));

```

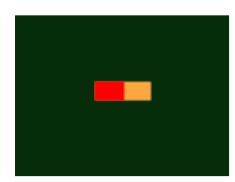

Draw rectangles with sizes of 5x25, 10x38 and 15x50 dimensions:

(Line width size is used for corner curvature, LINE\_WIDTH pixels are added in both directions in addition to the rectangle dimension):

```

//The VERTEX2F commands are in pairs to

define the top left and bottom right corners

of the rectangle.

dl( COLOR_RGB(128, 0, 0) );

dl ( LINE WIDTH (1 * 16) );

dl( BEGIN(RECTS) );

dl( VERTEX2F(28 * 16,38 * 16));

dl( VERTEX2F(33 * 16,63 * 16));

dl ( COLOR RGB (0, 128, 0) );

dl ( LINE WIDTH (5 * 16) );

dl( VERTEX2F(50 * 16,25 * 16) );

dl( VERTEX2F(60 * 16,63 * 16));

dl ( COLOR RGB (128, 128, 0) );

dl ( LINE WIDTH (10 * 16) );

dl( VERTEX2F(83 * 16, 13 * 16) );

dl ( VERTEX2F(98 * 16, 63 * 16) );

```

### Draw line strips for sets of coordinates:

```

dl( CLEAR_COLOR_RGB(5, 45, 110) );

dl( COLOR_RGB(255, 168, 64) );

dl( CLEAR(1 ,1 ,1) );

dl( BEGIN(LINE_STRIP) );

dl( VERTEX2F(5 * 16,5 * 16) );

dl( VERTEX2F(50 * 16,30 * 16) );

dl( VERTEX2F(63 * 16.50 * 16) );

```

### Draw Edge strips for above:

```

dl( CLEAR_COLOR_RGB(5, 45, 110) );

dl( COLOR_RGB(255, 168, 64) );

dl( CLEAR(1 ,1 ,1) );

dl( BEGIN(EDGE_STRIP_A) );

dl( VERTEX2F(5 * 16,5 * 16) );

dl( VERTEX2F(50 * 16,30 * 16) );

dl( VERTEX2F(63 * 16,50 * 16) );

```

### Draw Edge strips for below:

```

dl( CLEAR_COLOR_RGB(5, 45, 110) );

dl( COLOR_RGB(255, 168, 64) );

dl( CLEAR(1 ,1 ,1) );

dl( BEGIN(EDGE_STRIP_B) );

dl( VERTEX2F(5 * 16,5 * 16) );

dl( VERTEX2F(50 * 16,30 * 16) );

dl( VERTEX2F(63 * 16,50 * 16) );

```

Draw Edge strips for right:

```

dl ( CLEAR COLOR RGB (5, 45, 110) );

dl ( COLOR RGB (255, 168, 64) );

dl(CLEAR(1, 1, 1));

dl( BEGIN(EDGE STRIP R) );

dl ( VERTEX2F (\frac{5}{4} * \frac{16}{5} * \frac{16}{5} );

dl( VERTEX2F(50 * 16,30 * 16));

dl( VERTEX2F(63 * 16,50 * 16));

```

Draw Edge strips for left:

```

dl ( CLEAR COLOR RGB (5, 45, 110) );

dl ( COLOR RGB (255, 168, 64) );

dl(CLEAR(1, 1, 1));

dl( BEGIN(EDGE STRIP L) );

dl( VERTEX2F(5 * 16,5 * 16) );

dl( VERTEX2F(50 * 16,30 * 16));

dl( VERTEX2F(63 * 16,50 * 16));

```

#### **Bitmap Transformation Matrix** 2.10.5

To achieve the bitmap transformation, the bitmap transform matrix below is specified and denoted

```

m = \begin{bmatrix} BITMAP\_TRANSFORM\_A & BITMAP\_TRANSFORM\_B & BITMAP\_TRANSFORM\_C \end{bmatrix}

LBITMAP_TRANSFORM_D BITMAP_TRANSFORM_E BITMAP_TRANSFORM_F

```

by default m =  $\begin{bmatrix} 1.0 & 0.0 & 0.0 \\ 0.0 & 1.0 & 0.0 \end{bmatrix}$ , which is named as the **identity matrix**. The coordinates x' y' after transforming are calculated in the following equation:

$$\begin{bmatrix} x' \\ y' \\ 1 \end{bmatrix} = m \times \begin{bmatrix} x \\ y \\ 1 \end{bmatrix}$$

i.e.:

$$x' = x * A + y * B + C$$

$y' = x * D + y * E + F$

Where A,B,C,D,E,F stands for the values assigned by commands BITMAP TRANSFORM A-F.

### 2.10.6 Color and Transparency

The same bitmap can be drawn in more places on the screen, in different colors and transparency:

```

dl (COLOR RGB (255, 64, 64)); // red at (200, 120)

dl(VERTEX2II(200, 120, 0, 0));

dl(COLOR_RGB(64, 180, 64)); // green at (216, 136)

dl(VERTEX2II(216, 136, 0, 0));

dl(COLOR RGB(255, 255, 64)); // transparent yellow at (232, 152)

dl (COLOR A (150));

dl(VERTEX2II(232, 152, 0, 0));

```

Code Snippet 9 - Color and Transparency

Document Reference No.: BRT\_000225 Clearance No.: BRT#129

The COLOR\_RGB command changes the current drawing color, which colors the bitmap. If it is omitted, the default color RGB (255,255,255) will be used to render the bitmap in its original colors. The COLOR\_A command changes the current drawing alpha, changing the transparency of the drawing: an alpha of 0 means fully transparent and an alpha of 255 is fully opaque. Here a value of 150 gives a partially transparent effect.

#### 2.10.7 **Performance**

The graphics engine has no frame buffer: it uses a dynamic compositing method to build up each display line during scan out. Because of this, there is a finite amount of time available to draw each line. This time depends on the scan out parameters (decided by REG\_PCLK and **REG\_HCYCLE**) but is never less than 2048 internal clock cycles.

Some performance limits:

- The display list length must be less than 2048 instructions, because the graphics engine fetches display list commands at a rate of one per clock.

- The usual performance of rending pixels is 16 pixels per clock when the filter mode is in **NEAREST** mode, except for the following formats:

- TEXT8X8,

- **TEXTVGA**

- **PALETTED4444/565**

which renders 8 pixels per clock.

For **BILINEAR** filtered pixels, the drawing rate will be reduced to 1/4.

### To summarize:

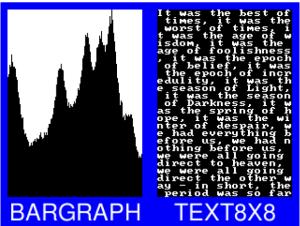

| Filter Modes | Bitmap Formats                          | Drawing Rate       |

|--------------|-----------------------------------------|--------------------|

| NEAREST      | TEXT8X8,                                | 8 pixel per clock  |

|              | TEXTVGA,                                |                    |

|              | PALETTED4444/565                        |                    |

| NEAREST      | The remaining formats not listed in the | 16 pixel per clock |

|              | row above                               |                    |

| BILINEAR     | TEXT8X8,                                | 2 pixel per clock  |

|              | TEXTVGA,                                |                    |

|              | PALETTED4444/565                        |                    |

| BILINEAR     | The remaining formats not listed in the | 4 pixel per clock  |

|              | row above                               |                    |

Table 6 - Bitmap Rendering Performance

# 3 Register Description

The registers are classified into the following groups according to their functionality:

- · Graphics Engine Registers,

- Audio Engine Registers,

- · Touch Engine Registers,

- Coprocessor Engine Registers,

- Special Registers,

- Miscellaneous Registers.

The detailed definition for each register is listed here. Most of registers are **32** bit wide and the special cases are marked separately. Reading from or writing to the reserved bits shall be always **zero**.

The bit fields marked  $\mathbf{r/o}$  are read-only.

The bit fields marked **w/o** are write only.

The bit fields marked  $\mathbf{r/w}$  are read-write.

The offset of registers are based on the address RAM\_REG.

# 3.1 Graphics Engine Registers

| REG_TAG Definition                                                                                                                         |                          |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 31 8                                                                                                                                       | 7 0                      |

| Reserved                                                                                                                                   | r/o                      |

| Offset: 0x7C                                                                                                                               | Reset Value: 0x0         |

| Bit 31 – 8: Reserved bits                                                                                                                  |                          |

| Bit 7 – 0: These bits are updated with the tag value. The tag value here is a touching point coordinator given in REG_TAG_X and REG_TAG_Y. | corresponding to the     |

| <b>Note:</b> Please note the difference between REG_TAG and REG_TOUCH_TAG.                                                                 |                          |

| REG_TAG is updated based on the X, Y given by REG_TAG_X and REG                                                                            |                          |

| REG_TOUCH_TAG is updated based on the current touching point cap                                                                           | tured from touch screen. |

### Register Definition 1 - REG\_TAG Definition

| REG_TAG_Y Definition          |            |    |                  |

|-------------------------------|------------|----|------------------|

| 31                            | 11         | 10 | 0                |

| Reserved                      |            |    | r/w              |

| Offset: 0x78                  |            |    | Reset Value: 0x0 |

| Bit 31 - 11: Reserved Bits    |            |    |                  |

| D': 40 0 TI I : I I I I I I I | V 1: 1 C.1 |    |                  |

Bit 10 – 0: These bits are set by the host as the Y coordinate of the touching point, which will enable the host to query the tag value. This register shall be used together with REG\_TAG\_X and REG\_TAG. Normally, in the case where the host has already captured the touching point's coordinate; this register can be updated to query the tag value of respective touching point.

## Register Definition 2 – REG\_TAG\_Y Definition

| REG_TAG_X Definition       |          |      |    |                  |

|----------------------------|----------|------|----|------------------|

| 31                         |          | 11   | 10 | 0                |

|                            | Reserved |      |    | r/w              |

| Offset: 0x74               |          |      |    | Reset Value: 0x0 |

| Bit 31 - 11: Reserved Bits | •        |      |    |                  |

|                            |          | <br> |    |                  |

Bit 10 – 0: These bits are set by the host as the X coordinate of the touching point, which will enable the host to query the tag value. This register shall be used together with REG\_TAG\_Y and REG\_TAG. Normally, in the case where the host has already captured the touching point's coordinate; this register can be updated to query the tag value of the respective touching point.

Register Definition 3 - REG\_TAG\_X Definition

| Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DRIBOTHO TECHNOLOGY                            | Document Reference No.: BRT_000225       | Clearance No.: BRT#1    | 129    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------|-------------------------|--------|

| Reserved    | REG PCLK Definition                            |                                          |                         |        |

| Reserved   r/w   Offset: 0x70   Reserved   r/w   Offset: 0x70   Reserved bits   Reserved bits   Reserved bits   Reserved bits are set to divide the main clock for PCLK. If the main clock is 60Mhz and the value of these bits are set to 5, the PCLK will be set to 12 MHz if these bits are set to zero, it means there is no PCLK output.  Register Definition 4 - REG_PCLK Definition  REG_PCLK_POL Definition  31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                | 8 7                                      |                         | (      |

| Bit 31 – 8: Reserved bits Bit 7 – 0: These bits are set to divide the main clock for PCLK. If the main clock is 60Mhz and the value of these bits are set to 5, the PCLK will be set to 12 MHz If these bits are set to zero, it means there is no PCLK output.  Register Definition 4 – REG_PCLK Definition  REG_PCLK_POL Definition 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Reserve                                        | d                                        | r/w                     |        |

| Bit 7 - 0: These bits are set to divide the main clock for PCLK. If the main clock is 60Mhz and the value of these bits are set to 5, the PCLK will be set to 12 MHz If these bits are set to zero, it means there is no PCLK output.  REG_PCLK POL Definition  REG_PCLK POL Definition Set value: 0x6  Bit 31 - 1: Reserved bits  Bit 0: This bit controls the polarity of PCLK. If it is set to zero, PCLK polarity is on the rising edge. If it is set to one, PCLK polarity is on the falling edge  Register Definition 5 - REG_PCLK_POL Definition  REG_CSPREAD Definition  REG_SWIZZLE Definition  REG_CSPREAD | Offset: 0x70                                   |                                          | Reset Value:            | 0x0    |

| value of these bits are set to 5, the PCLK will be set to 12 MHz If these bits are set to zero, it means there is no PCLK output.  Register Definition 4 - REG_PCLK Definition  REG_PCLK_POL Definition 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                |                                          |                         |        |

| Reg PCLK POL Definition  REG PCLK POL Definition  REG PCLK POL Definition  Reserved   1   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                |                                          |                         |        |

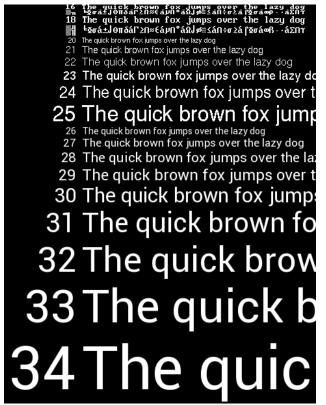

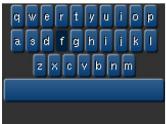

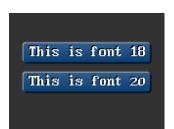

| REG_PCLK_POL Definition  31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                | will be set to 12 MHz If these bits a    | re set to zero, it me   | eans   |